# **Table of Contents**

Welcome from the Chair 49 **Papers** 3 4 **Governor's Welcome** 5 77 **Posters/Scientific Visualization Showcase Acknowledgements** 79 Research Posters 7 97 ACM Student Research Competition **General Information/SCinet 9 Registration and Conference Posters Store Hours 100 Scientific Visualization Showcase 9 Registration Categories 10 Registration Pass Access** 105 **Tutorials** 11 Exhibit Hall Hours 11 Information Booth Hours 117 Workshops 11 SC13 Preview Booth Hours **11 Social Events** 125 Birds of a Feather **12 Services/Facilities** 13 SCinet 145 **Awards** 151 **Exhibitor Forum 17 Map/Daily Schedules** 19 Downtown Area Map 21 Daily Schedules 163 Communities 165 HPC Educators 37 **Keynote/Invited Talks/Panels 169 Broader Engagement** 173 Doctoral Showcase 39 Keynote **39 Invited Talks 44 Panels**

# 5012

Salt Lake City, Utah

Welcome 3

#### Welcome from the Chair

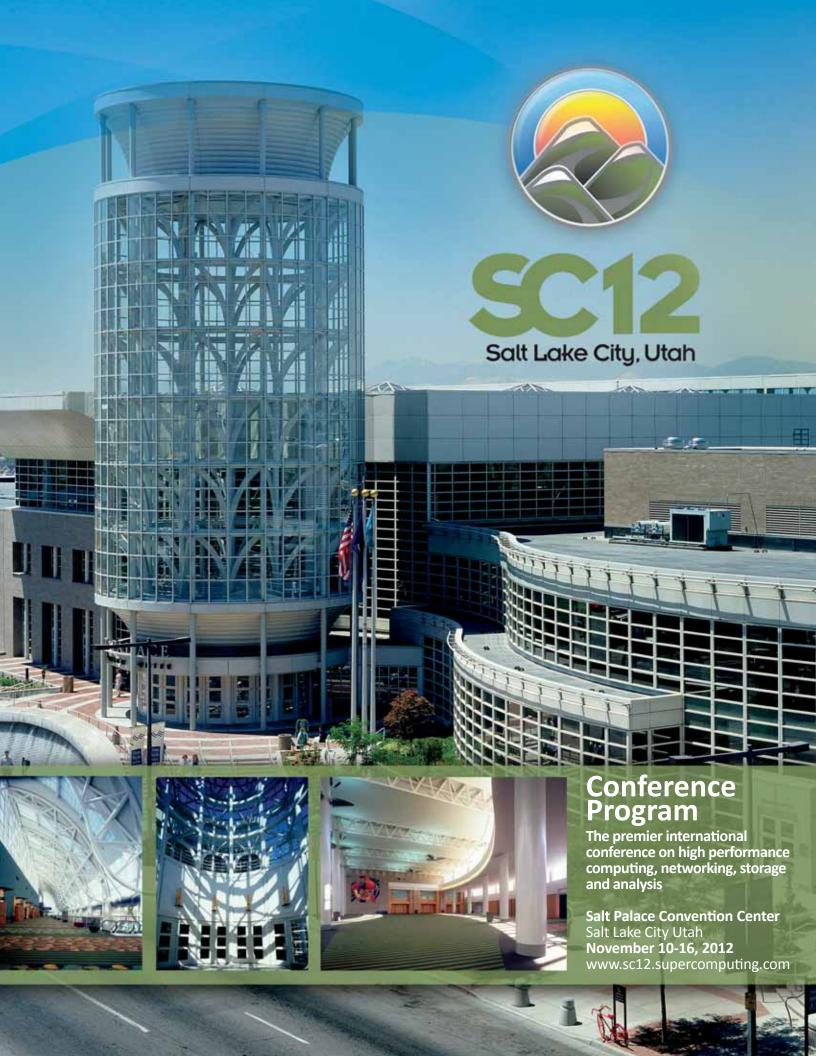

Welcome to Utah and to the 2012 conference (SC12) on high performance computing, networking, storage and analysis, sponsored by the IEEE Computer Society and the Association for Computing Machinery (ACM).

SC12 once again features a high quality technical program. We had a record 472 paper submissions and accepted 100 papers for presentation during the conference. In addition to papers, we have a great variety of invited talks, panels, posters and birds-of-a-feather sessions (BOFs) throughout the week. Bookending the conference will be tutorials on Sunday and Monday plus workshops on Sunday, Monday, and Friday. Nearly every part of the conference set records for submissions this year. The technical program committee has worked hard to select the best and most diverse program ever.

The focus of SC12 is on **you**—the conference attendee. We are working hard to make the conference more attendee friendly. To start, we have simplified the number of named activities at the conference. For example, the Keynote, plenary speakers and Masterworks are combined into one program called "Invited Talks." In addition, we are working to lay out the conference space with attendee needs as the highest priority. The Salt Palace Convention Center provides close access from the exhibit hall to the technical program rooms. To allow you to meet with colleagues, we have created three attendee lounges throughout the convention center to provide a place to sit down and recharge both yourself and your electronic devices. Finally, we are trying to make it easier to find activities and meetings. For example, rather than printed cardboard signs, most meeting rooms will have electronic signs which will always be up to date reflecting any last-minute changes.

The Exhibit hall houses a record number of exhibitors from a range of industry, academic, and government research organizations. SC's exhibit hall provides a unique market-place for not only commercial hardware and software, but also ways to see the latest science that is enabled by HPC. Connecting the exhibitors to each other and to the world beyond is SCinet, a unique blending of a high performance production network and a bleeding-edge demonstration network.

A distinctive aspect of SC is our commitment to developing the next generation of HPC professionals. This effort is focused in our Communities program. The rebranded HPC Educators program provides a high quality peer-reviewed program that describes how both HPC and scientific computation in general can be taught to students. The Educators program runs throughout the conference and is open to all technical program attendees. New for 2012 is the "Experience HPC for Undergraduates" program that provides an opportunity for talented sophomores and juniors to attend SC12 as well as have special sessions that introduce them to the field.

Thanks for attending and have a great conference!

Hollingsworth

Jeff Hollingsworth

SC12 General Chair

### STATE OF UTAH

GARY R. HERBERT GOVERNOR OFFICE OF THE GOVERNOR SALT LAKE CITY, UTAH 84114-2220 GREG BELL

LIEUTENANT GOVERNOR

November 10, 2012

#### Greetings!

As Governor of the great State of Utah, it is a pleasure to welcome you to SC12, the International Conference for High Performance Computing (HPC), Networking, Storage, and Analysis being held at the Salt Palace Convention Center in Salt Lake City, Utah.

Drawing more than ten thousand research and technology leaders from around the globe, SC12 represents an outstanding opportunity to meet new collaborators and experience the dramatic progress and innovation now underway in fields associated with computational science and engineering. This event provides participants a unique opportunity to explore the everchanging frontier of computing technology, and to delve further into fields like bio-computing, advanced manufacturing, sustainability, visualization, and the advancing internet.

I also invite you to enjoy our beautiful scenery - in both the Wasatch Mountains and our red rock canyons to the south – as well as the warm and friendly people in Utah. During your stay, I hope you experience some of the closely related technology leadership now taking place in Utah, as well as the favorable environment our state provides for both academic research and corporate innovation.

On behalf of the residents of Utah, best wishes for a successful and memorable event, and may you return soon.

Gary R. Herbert

Governor

Sincerely,

Acknowledgements 5

#### **Acknowledgements**

No conference this size could be possible without the dedication, commitment and passion of the SC12 committee. The core committee includes more than 100 people who have largely volunteered their time planning for this event for more than three years. Added to that number are the more than 500 people who have helped review submissions and contributed to the planning and preparations. The full list of committee members is posted on the conference website at sc12.supercomputing.org.

# SC12 Committee Management Conference Chair

Jeffrey K. Hollingsworth, University of Maryland

#### **Vice Chair**

Wilf Pinfold, Intel

#### **Deputy General Chair**

William Douglas Gropp, University of Illinois at Urbana-Champaign

#### **Executive Assistant**

Carolyn Peters, Argonne National Laboratory

#### **Communications Co-chairs**

Trish Damkroger, Lawrence Livermore National Laboratory Ian MacConnell, Ohio Supercomputer Center

#### **Communities Chair**

John Grosh, Lawrence Livermore National Laboratory

#### **Exhibits Chair**

Mary Hall, University of Utah

#### **Finance Chair**

Ralph A. McEldowney, DOD HPC Modernization Program

#### Infrastructure Chair

Janet Brown, Pittsburgh Supercomputing Center

#### **SCinet Chair**

Linda Winkler, Argonne National Laboratory

#### **Technical Program Chair**

Rajeev Thakur, Argonne National Laboratory

#### **Society Liaisons**

#### **IEEE-CS**

Lynne Harris Brookes Little Carmen Saliba

#### **ACM**

Donna Cappo

In this section you'll find information on registration, exhibit hours, conference store hours, descriptions and locations of all conference social events, information booths and their locations, and convention center facilities and services.

# General Information

#### **General Information**

#### **Registration and Conference Store**

The registration area and conference store are located in the South Foyer, Lower Concourse.

#### **Registration and Conference Store Hours**

| Saturday, November 10  | 1pm-6pm    |

|------------------------|------------|

| Sunday, November 11    | 7am-6pm    |

| Monday, November 12    | 7am-9pm    |

| Tuesday, November 13   | 7:30am-6pm |

| Wednesday, November 14 | 7:30am-6pm |

| Thursday, November 15  | 7:30am-5pm |

| Friday, November 15    | 8am-11am   |

#### **Registration Categories**

#### **Tutorials**

Tutorials run for two days, Sunday and Monday. Attendees can purchase a One-Day (Sunday or Monday) Passport or Two-Day (Sunday and Monday) Passport. The fee includes admission to any of the tutorials offered on the selected day for a One-Day Passport or a Two-Day Passport. The fee also includes a set of all of the tutorial notes (provided on a DVD) and lunch on the day(s) of Tutorial registration. Tutorial registration DOES NOT provide access to the keynote and exhibit halls.

#### **Technical Program**

Technical Program registration provides access to: the keynote, invited talks, papers, panels, posters (including reception), exhibits, Student Cluster Competition, awards, the Doctoral Research Showcase, Birds of a Feather, Exhibitor Forum, and Scientific Visualization Showcase (including reception), the Monday night Exhibits Opening Gala, Conference Reception on Thursday night, and one copy of the SC12 proceedings (on a DVD). In addition, registrants are admitted to the HPC Educators Program and Broader Engagement Program Tuesday through Thursday.

New for SC12: Workshops are NOT included with the Technical Program registration. If you would like to add workshops to your Technical Program registration, you will need to register for the Workshops Add-On. (See Workshops.)

#### **Exhibitor**

Exhibitor registration provides access to: the exhibit hall, the keynote, posters (except the poster reception), plenaries, awards, Exhibitor Forum, Student Cluster Competition, Friday panel sessions, and Scientific Visualization Showcase (but not related reception). The registration also includes access to the Exhibits Gala Opening on Monday evening and participation in the Exhibitor Reception.

#### **Exhibits Only**

Exhibits Only registration provides access to: The exhibit halls during regular exhibit hours, Tuesday through Thursday, posters (but not the poster reception), and the Awards ceremony (Thursday). It does NOT provide access to the Monday night Gala Opening or the Sunday evening Exhibitor Reception.

#### Workshops

New for SC12 are two categories for Workshops—Workshops Only and Workshops Add-On to Technical Program. This registration provides access to all Workshop sessions on the day(s) of registration. In addition, it provides access to the HPC Educators and Broader Engagement Programs on the day(s) of Workshop regisration.

#### **Proceedings**

Attendees registered for the Technical Program will receive one copy of the SC12 proceedings on a DVD.

#### **Lost Badge**

There is a \$40 processing fee to replace a lost badge.

#### **Age Requirements Policy**

- Technical Program attendees must be 16 years of age or older. Age verification is required.

- Exhibits-Only registration is available for children ages 12-16. Age verification is required.

- Children 12 and under are not permitted on the Exhibit Hall other than on Family Day (see below).

- Children under 16 are not allowed in the Exhibit Hall during installation, dismantling or before or after posted exhibit hours. Anyone under 16 must be accompanied by an adult at all times while visiting the exhibition.

#### **Family Day**

Family Day is Wednesday, November 14, 4pm-6pm. Adults and children 12 and over are permitted on the floor during these hours when accompanied by a registered conference attendee.

#### **Registration Pass Access**

Each registration category provides acccess to a different set of conference activities, as summarized below.

| Type of Event                                          | Tutorials | Technical<br>Program | Technical<br>Program<br>+Workshops | Workshop<br>Only | Exhibitor | Exhibit<br>Hall |

|--------------------------------------------------------|-----------|----------------------|------------------------------------|------------------|-----------|-----------------|

| Awards (Thursday)                                      |           | *                    | *                                  | *                | *         | *               |

| Birds-of-a-Feather                                     |           | *                    | *                                  |                  | *         |                 |

| Broader Engagement &<br>Educator Sessions<br>(Sun/Mon) |           |                      | *                                  | *                |           |                 |

| Broader Engagement & Educator Sessions (Tue-Thu)       |           | *                    | *                                  |                  |           |                 |

| Conference Reception<br>(Thursday)                     |           | *                    | *                                  |                  |           |                 |

| Exhibit Floor                                          |           | *                    | *                                  |                  | *         | *               |

| Exhibitor Forum                                        |           | *                    | *                                  |                  | *         |                 |

| Exhibits Gala Opening (Monday)                         |           | *                    | *                                  |                  | *         |                 |

| Exhibitor's Reception                                  |           |                      |                                    |                  | *         |                 |

| Invited Talks (Non-<br>Plenary)                        |           | *                    | *                                  |                  |           |                 |

| Invited Talks (Plenary)                                |           | *                    | *                                  |                  | *         |                 |

| Keynote (Tuesday)                                      |           | *                    | *                                  |                  | *         |                 |

| Panels (Tue-Thur)                                      |           | *                    | *                                  |                  |           |                 |

| Panels (Friday Only)                                   |           | *                    | *                                  |                  | *         |                 |

| Papers                                                 |           | *                    | *                                  |                  |           |                 |

| Posters                                                |           | *                    | *                                  |                  | *         | *               |

| Poster Reception<br>(Tuesday)                          |           | *                    | *                                  |                  |           |                 |

| Tutorial Lunch (Sun/Mon ONLY)                          | *         |                      |                                    |                  |           |                 |

| <b>Tutorial Sessions</b>                               | *         |                      |                                    |                  |           |                 |

| Student Cluster<br>Competition                         |           | *                    | *                                  |                  | *         |                 |

| Workshops                                              |           |                      | *                                  | *                |           |                 |

#### **Exhibit Floor Hours**

| Tuesday, Nov. 13   | 10am-6pm |

|--------------------|----------|

| Wednesday, Nov. 14 | 10am-6pm |

| Thursday, Nov. 15  | 10am-3pm |

#### **SC12 Information Booths**

Need up-to-the-minute information about what's happening at the conference. Need to know where to find your next session? What restaurants are close by? Where to get a document printed? These questions and more can be answered by a quick stop at one of the SC Information booths. There are two booth locations for your convenience: one is on the Lower Concourse, South Foyer, just near registration and the conference store; the second booth (satellite) is located on the Upper Concourse Lobby near Room 251.

#### SC12 Information Booth Hours

|           | Main Booth  | Satellite Booth |

|-----------|-------------|-----------------|

| Saturday  | 1pm-6pm     | Closed          |

| Sunday    | 8am-6pm     | 8am-5pm         |

| Monday    | 8am-7pm     | 8am-5pm         |

| Tuesday   | 7:30am-6pm  | 7:30am-5:30pm   |

| Wednesday | 8am-6pm     | 8am-5:30pm      |

| Thursday  | 8am-6pm     | 8am-Noon        |

| Friday    | 8:30am-12pm | Closed          |

#### **SC13 Preview Booth**

Members of next year's SC committee will be available in the SC13 booth (located in the South Foyer of the convention center) to offer information and discuss next year's SC conference in Denver. You'll also be greeted by the famous Blue Bear and a representative from the Denver Convention and Visitors Bureau who'll be able to answer questions about local attractions and amenities. Stop by for a picture with the Blue Bear and to pick up your free gift!

The booth will be open during the following hours:

| Tuesday, Nov. 12   | 10am-6pm |

|--------------------|----------|

| Wednesday, Nov. 13 | 10am-6pm |

| Thursday, Nov. 14  | 10am-6pm |

#### **Social Events**

Exhibitor Reception Sunday, November 11 6pm-9pm

SC12 will host an Exhibitor Reception for registered exhibitors. The party is SC12's way of thanking exhibitors for their participation and support of the conference. The reception will be held at The Hotel Elevate, a downtown nightclub located at 155 West 200 South, directly across the street from the South Entrance to the Salt Palace Convention Center. The Hotel Elevate boasts four separate bar areas, with a dance floor in the main bar. Exhibitors will be entertained by live bands, and food and drinks will be served throughout the event.

An Exhibitor badge and government-issued photo ID are required to attend this event, and attendees must be 21 years or older.

#### Exhibits Gala Opening Reception Monday, November 12 7pm-9pm

SC12 will host its annual Grand Opening Gala in the Exhibit Hall. This will be your first opportunity to see the latest high performance computing, networking, storage, analysis, and research products, services, and innovations. This event is open to all Technical Program and Exhibitor registrants.

Posters Reception Tuesday, November 13 5:15pm-7pm

The Posters Reception is an opportunity for attendees to interact with poster presenters. The reception is open to all attendees with Technical Program registration. The Poster Reception is located in the East Lobby.

#### Scientific Visualization Showcase Reception Tuesday, November 13 5:15pm-7pm

After you have viewed the posters at the Poster Reception, stop by the Scientific Visualization Showcase Reception for dessert. The reception is open to all attendees with Technical Program registration. The Poster Reception is located in the North Foyer.

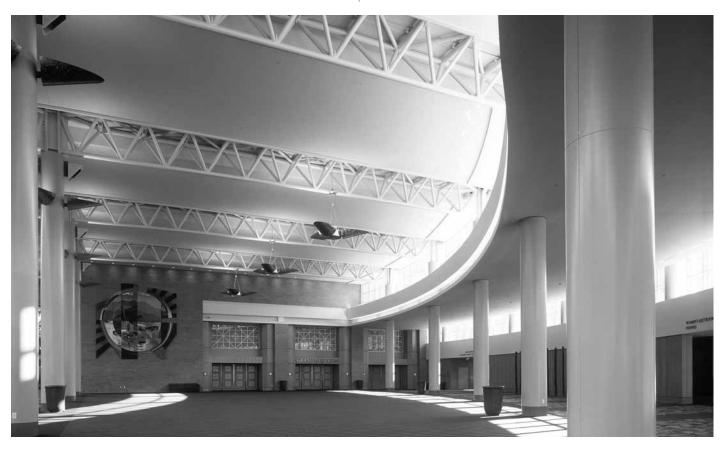

#### Technical Program Conference Reception Thursday, November 17 6pm-9pm

SC12 will host a conference reception for all Technical Program attendees. Join us for great food, beverages, and entertainment at The Depot (www.depotslc.com). The Depot, a lively nightclub located in an old train station, is only a few blocks from the convention center. There will be quiet rooms to get one last technical conversation in before heading home, as well as live entertainment, including two performances by comedian Ryan Hamilton.

Attendees are required to wear technical program badges throughout the reception, and badges may be checked during the event. In addition, all attendees will be required to present a photo ID (driver's license or passport) to enter this event and must be 21 years or older to consume alcohol.

Shuttle transportation to the event will run 7pm-10pm from the South Plaza Entrance of the convention center (look for buses with "The Depot" sign in the front window). Transportation also will be available for those on the hotel shuttle routes, with buses running every 15 minutes from the regular pick-up locations (again, look for "The Depot" sign in the front window).

#### Services/Facilities

#### **ATMs**

Two U.S. Bank cash machines are located inside the convention center. You'll find an ATM on the Upper Concourse (toward Room 254). Another is located in the North Foyer (near the rounded wall).

#### **Business Center**

The Salt Palace Business Center is located on the Upper Concourse of the convention center. The center is open most days from 8am to 6pm, but please call (801.534.6305) since, as of this printing, the hours had not been set to accommodate SC12.

#### **Coat and Bag Check**

Coat and Bag Check is located in the Lower Concourse, just outside the Ballroom. The hours are:

| Saturday, Nov. 10  | 1pm-6:30pm    |

|--------------------|---------------|

| Sunday, Nov. 11    | 7am-10pm      |

| Monday, Nov. 12    | 7:30am-9:30pm |

| Tuesday, Nov. 13   | 7:30am-7:30pm |

| Wednesday, Nov. 14 | 7:30am-6pm    |

| Thursday, Nov. 15  | 7:30am-9:30pm |

| Friday, Nov. 16    | 8am-1pm       |

#### **First-Aid Center**

There are two first aid offices in the convention center. One is on the east side, located next to Room 150A; the other is on the west side lobby, outside of Hall 4.

#### **Lost & Found**

Lost & Found is located in Room 258.

#### **Prayer and Meditation Room**

The Prayer and Meditation Room is located Room 260-B and is open Sunday-Thursday, 9am-5pm.

#### Restrooms

Restrooms are located conveniently throughout the convention center, as follows:

Lower level:

Halls A-E (located in the back)

Hall 1

Halls 4&5 (west side)

North and South Foyers

Outside Room 155

Upper level:

Across from 254B and near 255 Upper Mezzanine (on lefthand side)

#### Visitor's Center

The Visitor's Center is located near the East entrance. It is open daily from 9am-5pm.

#### Wheelchair Rental

Wheelchairs can be acquired through the Business Center.

#### Where Will SCinet Take You Next?

The era of data intensive science is only today in its infancy. Over the next decade, new large-scale scientific instruments will serve tens of thousands more scientists worldwide. Poised to create petabyte-scale data sets that need to be analyzed and archived, these experiments will need to rely on geographically-dispersed computational and storage resources.

For this reason, the SC conference series has since 1991 created SCinet, a leading edge, high-performance network, assembled each year to enable exhibitors and attendees of the conference to demonstrate HPC innovations in areas that rely on networking for success.

For SC12, SCinet will serve as one of the most powerful networks in the world with nearly 800 Gigabits per second (Gbps) in WAN capacity. Designed and built entirely by volunteers from universities, government and industry, SCinet will link the Salt Palace Convention Center to research networks around the world, such as the Department of Energy's ESnet, Internet2, National LambdaRail, KISTI, SURFnet and others.

SCinet serves as the platform for exhibitors to demonstrate the advanced computing resources of their home institutions and elsewhere by supporting a wide variety of bandwidth-driven applications including supercomputing, cloud computing and data mining. And unlike any commercial network provider, SCinet will utilize advanced virtual circuits and state-of-the-art measurement software that allow attendees and exhibitors to experience peak network performance at all times.

SCinet is also fostering developments in network research that will directly impact data-intensive science. The SCinet Research Sandbox (SRS), now in its third year of the SC conference, allows researchers to showcase "disruptive" network experiments in the unique, live environment of SCinet with access to over 100 Gbps of capacity and an OpenFlow-enabled testbed.

#### **SCinet Research Sandbox Participants**

#### **Efficient LHC Data Distribution across 100Gbps Networks**

The analysis of data leading to the recent discoveries at the Large Hadron Collider produces data flows of more than 100 Petabytes per year, and increasingly relies on the efficient movement of data sets between the globally distributed computing sites.

The team will demonstrate the state-of-the-art data movement tools, as enabling technology for high-throughput data distribution over 100Gbps WAN circuits. The demo will interconnect 3 major LHC Tier-2 computing sites and the SC12 show floor (booth 809) using 100Gbps technology.

Collaborating organizations: California Institute of Technology, University of Victoria, University of Michigan, with support from industry partners.

Demonstration booth: 809

# Exploiting Network Parallelism for Improving Data Transfer Performance

The task of scientific bulk data movement, e.g. migrating collected results from the instrumentation to the processing and storage facilities, is hampered by a lack of available network resources. Traditional R&E connectivity can be congested on portions of an end-to-end path causing degradation of overall performance. This SRS project will explore dynamic network control to facilitate efficient bulk data movement, combining opportunistic use of «traditional» networks with dedicated reservations over virtual circuits and OpenFlow enabled resources. The GridFTP application has been instrumented with the eXtensible Session Protocol (XSP), an intelligent system capable of controlling programmable networks. The project intends to show end to end performance improvement between the SC12 conference and campuses involved in the DYNES project, through a combination of regular connectivity, dynamic bandwidth allocations, TCP acceleration, and operations using multiple paths.

Collaborating organizations: Indiana University, Lawrence Berkeley National Laboratory, Argonne National Laboratory and Internet2

Demonstration booths: 1042, 1343

#### Multipathing with MPTCP and OpenFlow

This demo shows several emerging network technologies and how these can be used in big data transfers between data centres. In this demo traffic is sent simultaneously across multiple OpenFlow controlled paths between Geneva and Salt Lake City. The congestion control mechanism of Multipath TCP (MPTCP) favours the least congested paths and ensures that the load balancing across the paths is always optimal.

Collaborating organizations: SURFnet/SARA, Dutch Research Consortium, iCAIR and California Institute of Technology Demonstration booths: 2333, 809, 501

#### Multi-Science Science DMZ Model with OpenFlow

The emerging era of "Big Science" demands the highest possible network performance. End-to-end circuit automation and workflow-driven customization are two essential capabilities needed for networks to scale to meet this challenge.

This demonstration showcases how combining software-defined networking techniques with virtual circuits capabilities can transform the network into a dynamic, customer-configurable virtual switch. In doing so, users are able to rapidly customize network capabilities to meet their unique workflows with little to no configuration effort. The demo also highlights how the network can be automated to support multiple collaborations in parallel.

Collaborating organizations: ESnet, Ciena Corporation Demonstration booth: 2437

OpenFlow Enabled Hadoop over Local and Wide Area Cluster

The Hadoop Distributed File Systems and Hadoop's implementation of MapReduce is one of the most widely used platforms for data intensive computing. The shuffle and sort phases of a MapReduce computation often saturate network links to nodes and the reduce phase of the computation must wait for data. Our study explores the use of OpenFlow to the control network configuration for different flows and thereby provide different network characteristics for different categories of Hadoop traffic. We demonstrate an OpenFlow enabled version of Hadoop that dynamically modifies the network topology in order to improve the performance of Hadoop.

Collaborating organizations: University of Chicago Demonstration booth: 501

OpenFlow Services for Science: An International Experimental Research Network Demonstrating Multi-Domain Automatic Network Topology Discovery, Direct Dynamic Path Provisioning Using Edge Signaling and Control, Integration With Multipathing Using MPTCP

Large-scale data intensive science requires global collaboration and sophisticated high capacity data management. The emergence of more flexible networking, for example, using techniques based on OpenFlow, provides opportunities to address these issues because these techniques enable a high degree of network customization and dynamic provisioning. These techniques enable large-scale facilities to be created that can be used to prototype new architecture, services, protocols, and technologies. A number of research organizations from several countries have designed and implemented a persistent international experimental research facility that can be used to prototype, investigate, and test network innovations for largescale global science. For SC12, this international experimental network facility will be extended to from sites across the world to the conference showfloor, and it will be used to support several testbeds and to showcase a series of complementary demonstrations.

Collaborating organizations: International Center for Advanced Internet Research Northwestern University; National Center for High-Performance Computing, Taiwan; University of Applied Sciences, Taiwan; National Cheng-Kung University, Taiwan; SARA, The Netherlands, California Institute of Technology/CERN; SURFnet. The Netherlands Demonstration booths: 2333, 501, 843, 809

# Reservoir Labs R-Scope®: Scalable Cyber-Security for Terabit Cloud Computing

Reservoir Labs will demonstrate R-Scope®, a scalable, highperformance network packet inspection technology that forms the core of a new generation of Intrusion Detection Systems enabling the construction and deployment of cyber security infrastructures scaling to terabit per second ingest bandwidths. This scalability is enabled by the use of low-power and highperformance manycore network processors combined with Reservoir's enhancements to Bro, including the incorporation of new sophisticated data structures such as LF- and TED queuing. The innovative R-Scope CSC80 appliance, implemented on a 1U Tilera TilExtreme-Gx platform, will demonstrate the capacity to perform cyber-security analysis at 80Gbps, by combining cyber-security aware front-end network traffic load balancing tightly coupled with the full back-end analytic power of Bro. This fully-programmable platform incorporates the full Bro semantics into the appliance's load-balancing front-end and the back-end analytic nodes.

Collaborating organizations: Reservoir Labs, SCinet Security Team

#### **SC12** Wireless Access Policy

In addition to high performance exhibit floor connectivity, SCinet will deploy IEEE 802.11a, 802.11g and 802.11n wireless networks throughout the Salt Palace Convention Center (SPCC) in Salt Lake City. These wireless networks are part of the commodity SCinet network, providing basic access to the Internet. The wireless network will be provided in the meeting rooms, exhibit halls, and common areas of the SPCC. The network can be accessed via SSIDs "SC12" or "eduroam".

eduroam (education roaming) allows users (researchers, teachers, students, staff) from participating institutions to securely access the Internet from any eduroam-enabled institution. The eduroam principle is based on the fact that the user's authentication is done by the user's home institution, whereas the authorization decision granting access to network resources is done by the visited network.

SCinet provides the wireless network for use by all exhibitors and attendees at no charge. Users may experience coverage difficulties in certain areas due to known wireless network limitations, such as areas of reduced signal strength, network congestion, limited client capacity, or other coverage problems. Please watch for additional signage at appropriate locations throughout the convention center. Network settings including IP and DNS addresses for wireless clients are provided by SCinet DHCP services. Laptops and other wireless devices configured to request network configuration information via DHCP receive this information automatically upon entering the SCinet wireless coverage area.

SCinet will monitor the health of the wireless networks and maintain this information for exhibitors and attendees. The SCinet wireless networks are governed by this policy posted on the SC12 conference Web site. In summary, while every practical effort shall be made to provide stable reliable network services, there is no explicit service level agreement for any SCinet network, including the wireless networks, nor are there any remedies available in the event that network services are lost.

In order to provide the most robust wireless service possible, SCinet must control the entire 2.4GHz and 5.2GHz ISM bands (2.412GHz to 2.462GHz and 5.15GHz to 5.35GHz) within the SPCC where SC12 conference events are taking place. This has important implications for both exhibitors and attendees:

- Exhibitors and attendees *may not* operate their own IEEE 802.11 (a,b,g,n or other standard) wireless Ethernet access points anywhere within the convention center, including within their own booth.

- Wireless clients may not operate in ad-hoc or peer-to-peer mode due to the potential for interference with other wireless clients.

- Exhibitors and attendees may not operate 2.4GHz or 5.2GHz cordless phones or microphones, wireless video or security cameras, or any other equipment transmitting in the 2.4GHz or 5.2GHz spectrum.

SCinet wants everyone to have a successful, pleasant experience at SC12. This should include the ability to sit down with your wireless-equipped laptop or PDA to check e-mail or surf the Web from anywhere in the wireless coverage areas. Please help us achieve this goal by not operating equipment that will interfere with other users.

SCinet will actively monitor both the 2.4GHz and 5.2GHz frequency spectrums and reserves the right to disconnect any equipment that interferes with the SCinet wireless networks. The SC12 conference reserves the right to deny or remove access to any system in violation of the SCinet acceptable usage policy. Disruptive or illegal activities will not be tolerated.

SCinet reserves the right to revoke access to the wireless network to anyone who uses multicast applications or harms the network in any way, intended or unintended, via computer virus, excessive bandwidth consumption or similar misuse.

Remember that the SCinet wireless network is a best effort network. If you are running demonstrations in your booth that require high availability network access, we advise exhibitors to order a wired network connection.

#### **SCinet Collaborators**

SCinet is the result of the hard work and significant contributions of many government, research, education and corporate collaborators. Collaborators for SC12 include:

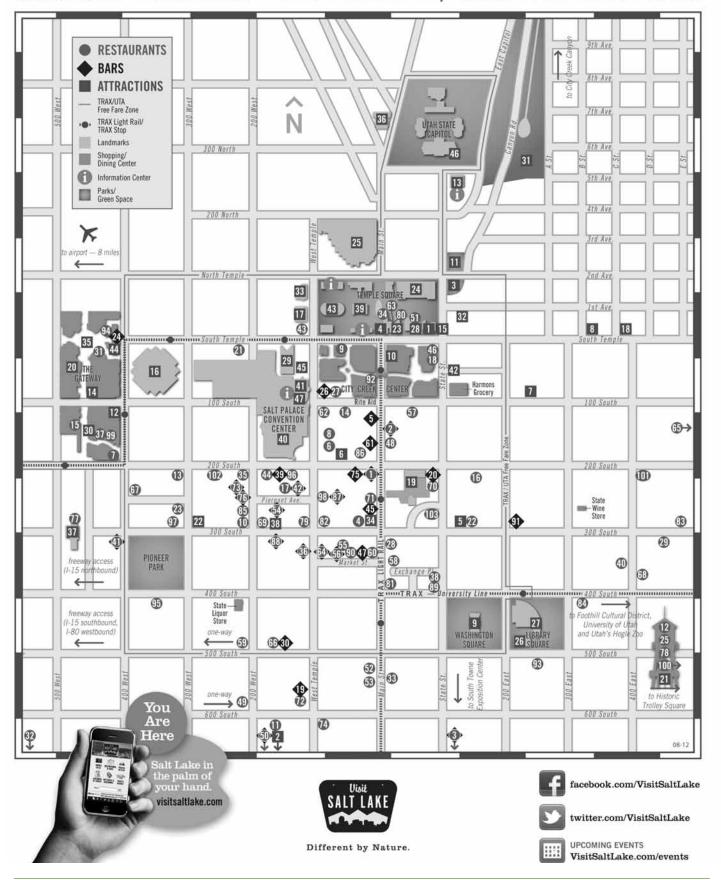

Map Downtown Area 19

# Salt Lake Downtown RESTAURANTS, BARS & ATTRACTIONS

# Salt Lake Downtown

#### Visit Salt Lake

90 South West Temple, Salt Lake City, Utah 801-534-4900 info@visitsaltlake.com VisitSaltLake.com

| RI           | ESTAURANTS &                             | BARS         |

|--------------|------------------------------------------|--------------|

| <b>ŵ</b>     | Bambara                                  | 801-363-5454 |

| <b>@</b>     | Bayleaf Bar & Grub                       | 801-359-8490 |

| <b>√</b> Ô•  | The Bayou                                | 801-961-8400 |

| 0            | Beehive Tea Room & Wedding Library       | 801-328-4700 |

| •            | Beerhive Pub                             | 801-364-4268 |

| 0            | Benihana                                 | 801-322-2421 |

| 0            | Biaggi's Ristorante Italiano             | 801-596-7222 |

| 0            | Blue Iguana Restaurant                   | 801-533-8900 |

| 0            | Blue Lemon                               | 801-328-2583 |

| 1            | Buca di Beppo                            | 801-575-6262 |

| •            | Cafe Olympus                             | 801-521-7373 |

| <b>O</b>     | Cafe SuperNatural                        | 801-363-1000 |

| ®            | Cafe Trang                               | 801-359-1638 |

| 0            | Caffe Molise                             | 801-364-8833 |

| (B)          | Canyon Creek Cafes Food Court            |              |

| 1            | Cedars of Lebanon                        | 801-364-4096 |

| •            | Christopher's Seafood & Steakhouse       | 801-519-8515 |

| •            | City Creek Center Food Court             |              |

| •            | Clouseau's                               | 801-359-7800 |

| 1            | Club Piastra                             | 801-961-8700 |

| <b>a</b>     | Copper Canyon Grill House & Tavern       | 801-521-7800 |

| @            | Copper Onion                             | 801-355-3282 |

| @            | Cucina Toscana                           | 801-328-3463 |

| 4            | The Depot                                | 801-456-2800 |

| <b>(B)</b>   | Desert Edge Brewery at the Pub           | 801-521-8917 |

| 4            | Destinations                             | 801-531-0800 |

| 0            | Elevations Restaurant                    | 801-537-6019 |

| <b>@</b>     | Eva                                      | 801-359-8447 |

| <b>49</b>    | Faustina                                 | 801-746-4441 |

| •            | First Press                              | 801-401-2000 |

| 0            | Fleming's<br>Prime Steakhouse & Wine Bar | 801-355-3704 |

| 0            | Frida Bistro                             | 801-983-6692 |

| <b>®</b>     | The Garden Cafe                          | 801-258-6708 |

| <b>3</b>     | The Garden Restaurant                    | 801-539-3170 |

| <b>3</b>     | Ginza Japanese Cuisine & Sushi Bar       | 801-322-2224 |

| <b>®</b>     | Gracie's                                 | 801-819-7565 |

| Ō            | Happy Sumo At Gateway                    | 801-456-7866 |

| <b>③</b>     | Himalayan Kitchen                        | 801-328-2077 |

| •            | The Hotel Bar & Nightclub                | 801-487-4310 |

| 0            | Ichiban Sushi & Japanese Cuisine         | 801-532-7522 |

| <b>(Ĵ)</b> ▶ | Iggy's Sports Grill                      | 801-532-9999 |

| (În          | Inferno Cantina                          | 801-883-8838 |

| (3)          | JB's Family Restaurant                   | 801-328-8344 |

| 0            | J. Wong's Asian Bistro                   | 801-350-0888 |

| <b>(</b>     | Keys On Main                             | 801-363-3638 |

| <b>(1)</b>   | Kneader's Bakery and Cafe                | 801-428-3051 |

| <b>1</b>     | Kristauf's Martini Bar                   | 801-366-9490 |

| <b>®</b>     | Lamb's Grill Cafe                        | 801-364-7166 |

| <b>®</b>     | Last Samurai Japanese Steakhouse         | 801-596-2293 |

| 4            | Legends Pub & Grill                      | 801-355-3598 |

| 1            | The Lion House Pantry Restaurant*        | 801-363-5466 |

|              |                                          |              |

| <b>®</b>    | Little America Coffee Shop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 801-596-5700 |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| 3           | Little America Steak House                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 801-596-5700 |

| (B)         | Lumpys Downtown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 801-938-3070 |

| <b>3</b>    | Market Street Grill - Downtown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 801-322-4668 |

| (Î)         | Market Street Oyster Bar - Downtown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 801-531-6044 |

| 1           | Martine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 801-363-9328 |

| <b>5</b>    | Maxwell's East Coast Eatery                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 801-328-0304 |

| 69          | McDonald's                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 801-364-1614 |

| 60          | The Melting Pot                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 801-521-6358 |

| •           | Murphy's Bar and Grill                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 801-359-7271 |

| 1           | Naked Fish Japanese Bistro                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 801-595-8888 |

| 63          | Nauvoo Cafe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 801-539-3346 |

| (Î)         | New Yorker                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 801-363-0166 |

| (1)         | Oasis Cafe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 801-322-0404 |

| 63          | Olio Ristorante                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 801-323-7575 |

| 1           | Pallet Bistro                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 801-935-4431 |

| 633         | Papa John's Pizza                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 801-521-7272 |